NEDO

半導体後工程における微細な配線形成工程をマスクレス化で短縮し、高性能な先端半導体パッケージの製造コスト低減に貢献します

NEDOは、委託事業である「省エネエレクトロニクスの製造基盤強化に向けた技術開発事業」(以下、本事業)の一環として、半導体製造装置の高度化に取り組んでいます。このたび、株式会社オーク製作所は、フォトマスクを使用せず、半導体基板に回路パターンを焼き付けるダイレクト露光装置で、従来よりも高い解像性および位置合わせ精度を実現可能な次世代技術と、その技術を搭載した装置(以下、本装置)を開発しました。これにより、チップレット集積技術で大型化が進んでいる先端半導体パッケージ(以下、先端パッケージ)などで、高い位置合わせ精度や補正技術が要求される微細な配線回路形成に、ダイレクト露光技術が適用可能であることを実証しました。

今後、本装置を2025年度内に製品化し、省エネルギー化の鍵となる先端パッケージの製造基盤の強化、安定供給および製造コストの低減に貢献します。

1.背景

産業のIoT化や電動化の進展に伴い、あらゆる電子機器に搭載されている半導体は、高性能化とともに省エネルギー化が求められています。例えば、最近急速に発展、普及している人工知能(AI)技術は、莫大(ばくだい)なデータを高速に処理する必要があり、その処理を担うAIデータセンターには高い処理能力ながら低消費電力が要求されることから、高性能な先端半導体を搭載した演算処理装置が不可欠です。

一方、高性能化を実現してきた従来の半導体の微細化技術が物理的・経済的な限界を迎える中で、半導体回路を機能単位に小さく分割し、おのおの最適な技術で製造する、「チップレット集積技術」が着目されてきました。この実現のためには、半導体を組み合わせ、横並びに実装(2.xD)し、垂直方向に積層(3D)して高集積化する半導体後工程のパッケージング技術が必要不可欠となり、各層の位置を正確に合わせるアライメント技術、隙間なく重ね合わせる接合技術、積層したチップを高精度で相互に配線接続する技術など、高度な製造技術が求められます。

このような背景の下、NEDOは、半導体製造装置の高度化に向けた開発に取り組んでいます。その一環として、2022年度から本事業※1で先端パッケージに求められる微細回路パターンを焼き付ける露光装置のうち、回路パターンを転写するための原版であるフォトマスクを使用しないダイレクト露光装置の高度化に向けた開発を、オーク製作所と共同で進めてきました。

ダイレクト露光装置は、フォトマスクの設計や製造にかかる時間とコストを削減し、先端パッケージの開発期間の短縮や量産時のプロセス効率化を可能とする特徴があります。しかし、先端パッケージの製造に適用するには、配線を微細化するための解像性や、正確な位置に露光するための位置合わせ精度の向上が必要でした。

2.今回の成果

(1)高解像度化技術の開発

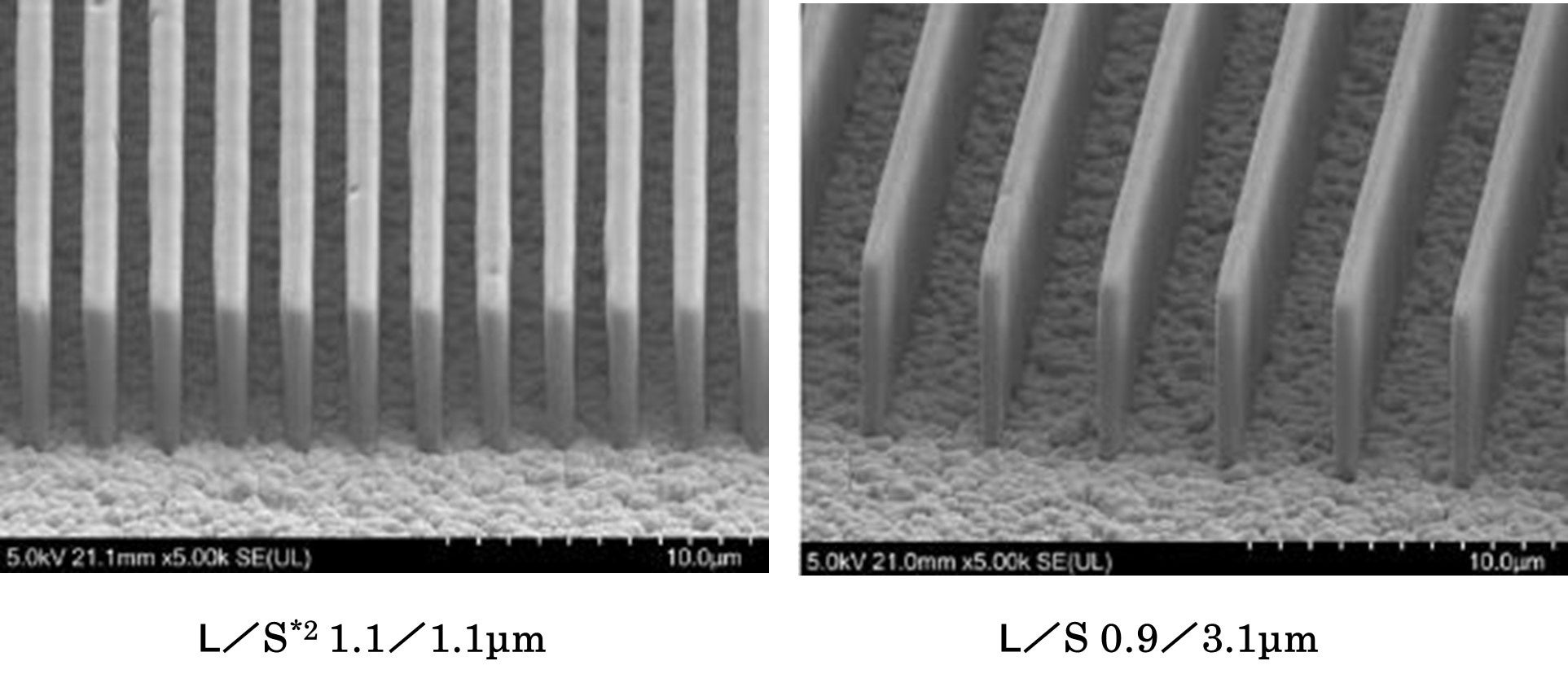

本事業でオーク製作所は、フォトマスクデータに従って空間光変調素子を高速で制御する技術と、高解像光学系を開発し、回路基板上の感光性材料に線幅1μmの回路を形成することに成功しました。

(感光性材料への回路パターン焼き付けおよび現像後走査型電子顕微鏡写真)

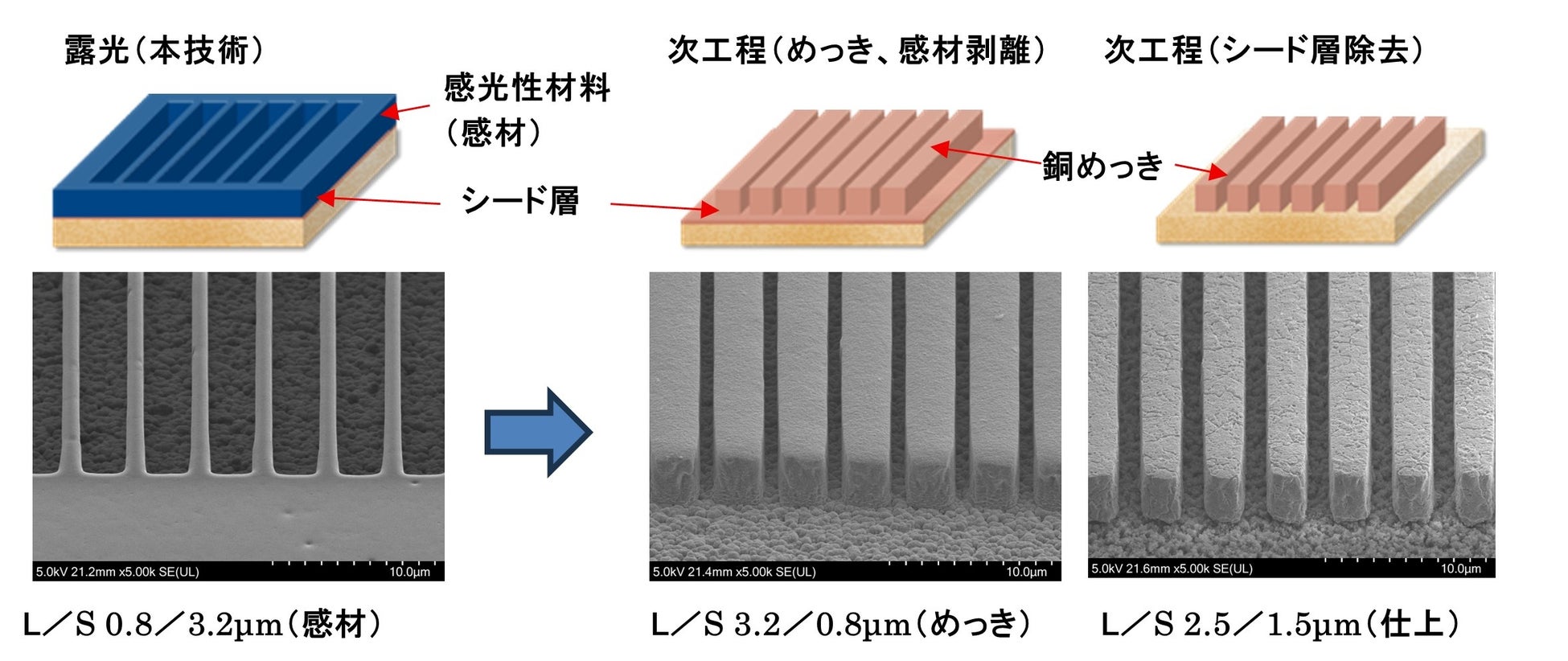

(2)微細めっき配線形成への適用性実証

今回開発した微細化技術により、有機材料上で線幅2μmの銅めっき配線形成が実現可能である事を確認しました。

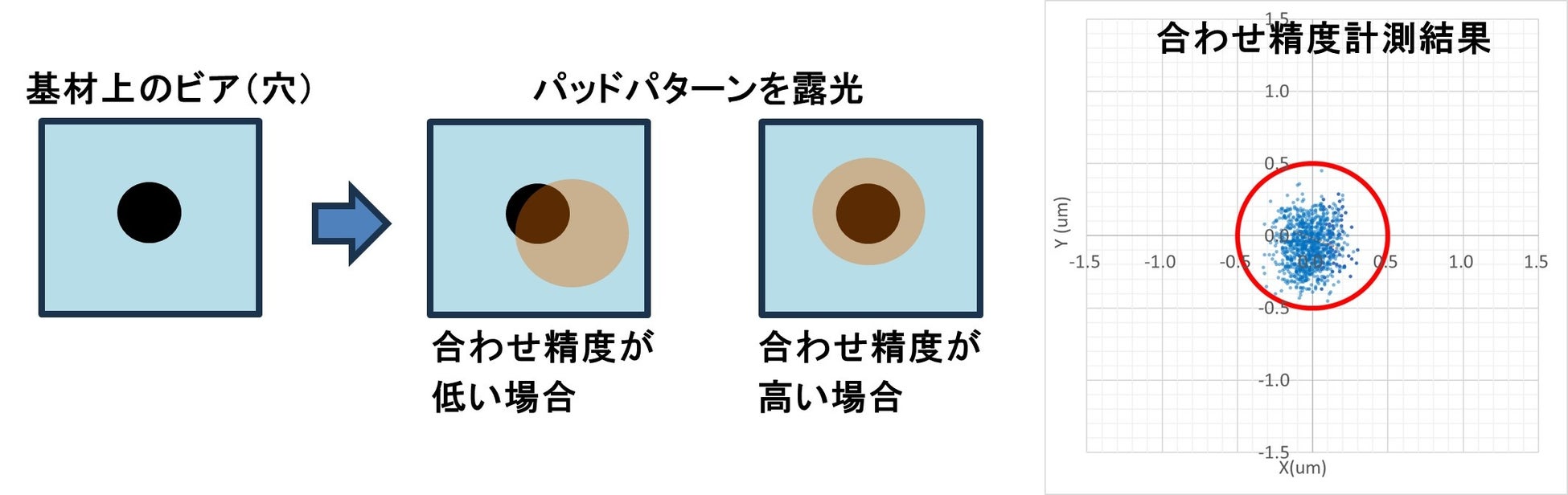

(3)位置合わせ精度の向上

位置合わせ精度は、設計座標値に対してどこまで正確に回路パターンを配置できるかの指標で、配線が微細化するほど、要求が厳しくなります。さらに、有機材を用いる先端パッケージでは、基材の伸縮に応じて露光するデータを補正する技術が求められます。このため、高精度で繰り返し再現性に優れた本体ステージとともに、基材上のアライメントマーク*3を読み取る高精度カメラでのリアルタイム位置補正技術を開発しました。これにより、510×515mm*4の露光サイズ全面に対して0.5μmの精度で回路パターンの配置が可能となりました。

(4)ダイバイダイ・アライメント*5技術の開発

先端パッケージには、複数の配線接続用チップを中間基板であるインターポーザ内に埋め込み、その上に実装する半導体チップ同士を電気的に接続するタイプがあります。その際、埋め込んだ接続チップの実際の位置と設計上の位置とのズレであるダイシフトが発生するため、それに対応した露光位置の補正が必要となります。オーク製作所は、リアルタイム位置補正技術を応用して、ダイシフトに対応可能なダイバイダイ・アライメント技術を開発しました。

3.今後の予定

オーク製作所は、本装置を2025年度内に製品化するとともに、2025年度から2026年度にかけてシリーズ化を目指します。これにより、先端パッケージに関して多様化する顧客要求への対応と、省エネルギー化の鍵となる先端パッケージの製造基盤の強化、安定供給および製造コストの低減に貢献します。また、さらに性能を向上させた改良機の開発を継続し、進化する市場要求にも対応していきます。

【注釈】

※1 本事業

事業名:省エネエレクトロニクスの製造基盤強化に向けた技術開発事業/半導体製造装置の高度化に向けた開発/三次元積層関連の革新的な後工程用露光装置の研究開発

事業期間:2022年度~2025年度

事業概要:省エネエレクトロニクスの製造基盤強化に向けた技術開発事業

https://www.nedo.go.jp/activities/ZZJP_100192.html

※2 L/S

Line&Spaceの略で、回路パターンの幅(Line)と、隣接するパターン間の間隔(Space)を示しています。

※3 アライメントマーク

アライメント(位置合わせ)を行うための目印となるパターンのことです。

※4 510×515mm

SEMI規格(SEMI3D20)で定義されたパネルレベルパッケージの標準サイズの一つです。

※5 ダイバイダイ・アライメント

基板上に再配置された個別のダイの実際の位置を正確に検出し、焼き付けるパターンを、その位置に整合するように補正する技術です。